Možno ale podľa inej zmienky že DIY komunita na týchto postupoch pracuje spoločne, len komusi došla trpezlivosť a rozhodol sa skoncovať so stávajúcou realitou "Koho čipy spájkuješ, toho pesničku spievaj"

Tomuhle jsem se musel upřímně zasmát.

Realita je taková, že polovodičový průmysl posledních několik let prochází "implozí", kdy se slučuje kdekdo do jednoho velkého koglomerátu. Milimetr čtvereční na waferu stojí skoro stejně, jestli na něm udělám jednu výkonovou diodu, nebo tisíc tranzistorů, z výrobní technologie se stala komodita - velice podobně jako je komodita výroba plošných spojů (byť komplexitou technologie je to pořád o pár stupňů někde jinde).

Analogařina je limitována ztrátovým výkonem a šumem vs. plocha a miniaturizovat nejde a nepude (spousta analogových obvodů se vyrábí doteď na linkách které jsou postaveny v sedmdesátých), optimalizuje se jen stabilita výrobních procesů a nadstavby nad rámec základní technologie čipu (např. přesné tenkovrstvé rezistory jako extra vrstva). Stejné platí pro I/O digitálních obvodů - linkové budiče a integrovaná ESD ochrana bude vždy potřebovat danou plochu a nejde zminiaturizovat, protože výkonová ztráta na plochu je pevně daný limit přes který se nedá jít.

Digitálka je u spodního konce složitosti mnohem ekonomičtější na FPGA i v relativně velkých objemech a tahle hranice se posouvá stále dál a dál do oblasti, kde původně šly realizovat jen zakázkovým obvodem.

Exponencionální nárůst ceny litografických masek se zmenšující se geometrií dost jasně omezuje doménu toho, jak dalece se dá s hustotu integrace zajít a že je to něco, co je v dosahu pouze řádově jednotek nadnárodních korporací. Útěchou může být, že pod ně patří i Xilinx a ex-Altera, nyní už Intel.

Hlavní bariérou pro "malé ryby" a hobbíky vůbec nejsou výrobní technologie, ale návrhové prostředky. Pokud nemáte v čem načíst designkit od zvolené fabriky, udělat návrh schématu, odsimulovat, layout a export databáze, je vám snění o vlastních čipech stejně k ničemu. A při zjištění cen těhle nástrojů by se tady většině třikrát protočily panenky. Opensource nástroje jsou naprosto tragické a téměř nepoužitelné (rozhodně ne pro komerční práci). Asi nemusím podotýkat jak na tom bude s charakterizací a stabilitou procesu na koleni ušmudlaná technologie pro výrobu ve srovnání s komerčním sektorem.

Pool servisy přístupné všem pro prototypové čipy a školní projekty existují už dlouhé roky, například:

https://mycmp.fr/technologies/price-list.html

https://www.ihp-microelectronics.com/en ... -list.html

Těch pár tisíc euro za mm2 při 20 kusech čipu bez validace funkce jsou pořád pakatel ve srovnání s tím, kolik stojí licence nástrojů k návrhu a na kolik příjde následná výroba sady litografických masek pro sériovou výrobu a příprava pro výrobní testery. A testování před a po pouzdření je dost podstatnou součástí celého příběhu.

Další problém je to, že komoditní technologie na větších nodech nejsou optimalizované pro precizní práci v analogovém režimu a není tedy šance se ani vzdáleně přiblížit parametry k tomu, co dosahují renomovaní výrobci i v rámci lacincých čipů (vlastní staré výrobní linky si piplají z dobrého důvodu).

Objemy pro které se tohle vyplatí jsou dost mimo rámec toho, ve kterém operuje většina technologických firem zasahujících záběrem do elektroniky - jediná výjimka nastvá v případě nějaké podstatné přidané hodnoty, nebo nemožnosti daný problém řešit z diskrétních obvodů v rámci integrace na DPS, nebo syntézou ve FPGA.

===

Mimochodem - prvenství v na koleni ušmudlaném solid state polovodiči (a taky bez vzdělání v oboru) má myslím madam Ellsworth.

https://www.youtube.com/playlist?list=P ... 97C1C07A2D

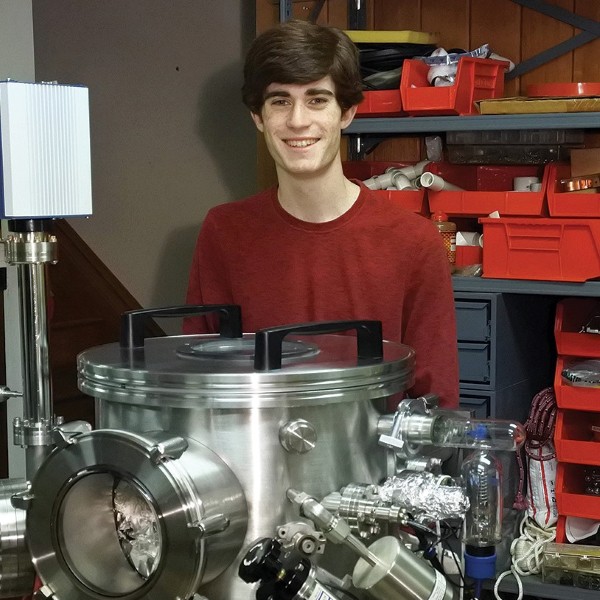

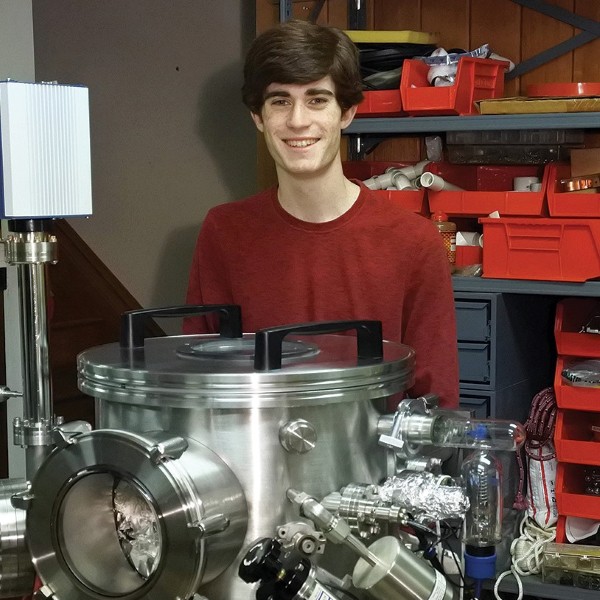

Primárně je to o tom, že dotyčný vyhrál v loterii toho, jak se šikovně narodit. Ani zájem samotný, ani inteligence, ani investované hodiny času nad studiem samy o sobě neznamenají vůbec nic, pokud neexistuje i materiální zázemí na které si dost očividně nevydělal jen vlastníma rukama.